「チップレット集積」とは、半導体の設計と製造における比較的新しい概念です。このアプローチでは、複数の小さなチップ(チップレットと呼ばれる)を組み合わせて、一つの大きな機能的なデバイスを構築します。この手法は、従来の大きな単一チップの設計に代わるものとして注目されています。

チップレット技術の主な利点は以下の通りです:

- 柔軟性とスケーラビリティ: 異なる種類のチップレットを組み合わせることで、カスタマイズされた機能を持つデバイスを効率的に設計できます。また、需要に応じて製品をスケールアップまたはスケールダウンすることが可能です。

- 製造コストの削減: 小さいチップレットは、大きなチップよりも製造しやすく、歩留まりが良いため、コスト削減に繋がります。

- 高性能化: さまざまな専門化されたチップレットを組み合わせることで、単一の大きなチップよりも高い性能を達成できる場合があります。

- 設計の簡素化: 小さなチップレットを使用することで、設計プロセスが簡素化され、製品の市場投入までの時間が短縮される可能性があります。

ただし、チップレット技術は、チップ間の通信や組み立てに関する技術的な課題も抱えています。これらのチップレットを効果的に結合し、高速かつ信頼性の高いデータ伝送を実現するためには、高度なインターコネクト技術が必要です。また、異なるチップレット間での互換性の確保も重要な要素となります。

今後、この技術は、コンピューティング、ネットワーキング、ストレージなど、さまざまな分野での応用が期待されています。

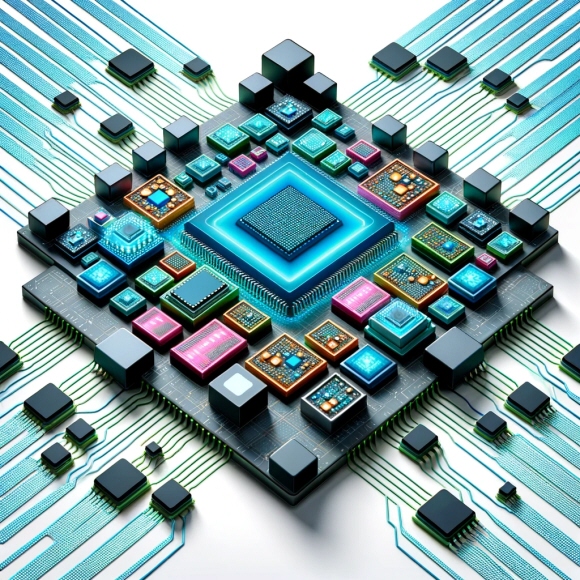

チップレット集積のコンセプトを表現したイラストです。このイメージでは、複数の小さなチップ(チップレット)が組み合わさって、より大きな複雑な統合回路を形成しています。それぞれのチップレットが異なる色と形で表現されており、その多様な機能と設計を示しています。チップレット技術のモジュラーな性質、柔軟性、スケーラビリティ、そして性能向上がこのイラストを通じて示されています。

|

| <トップページへ> |